DDR3入门系列二-DDR3硬件电路及Xilinx-MIG-IP核介绍

目录

DDR3入门系列(二)——DDR3硬件电路及Xilinx MIG IP核介绍

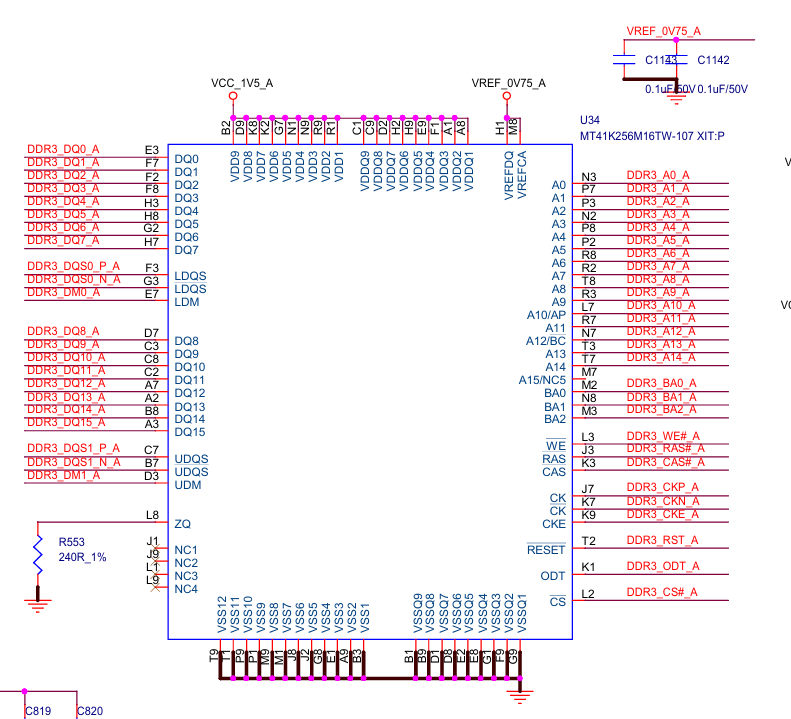

1. 以FPGA作为控制器的DDR硬件电路

下图提供一种DDR3与FPGA硬件连接的参考电路,DDR3型号为MT41K256M16xx。

2. 赛灵思(Xilinx)MIG IP核的介绍

Mig(memory interface generator)IP核,是Xilinx官方提供的存储器接口控制器IP核,在Vivado软件的IP Catalog界面中可以搜索得到。双击进入该IP核GUI界面之后,先确认好FPGA型号。这里可以自己在电脑上对照着学。

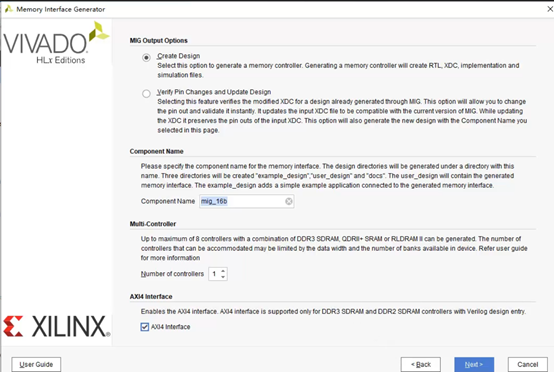

点击Next后看到下一个界面:

MIG Output Options:输出选项,一般选择Create Design就行。

Component Name:组件名称,设置该界面下生成的模块的名称。

Multi-Controller:支持多个DDR控制器,根据实际需要选择。

AXI4 Interface:选择启用AXI4接口,适合CPU随机访问存储器里的地址。

点击Next后看到下一个界面:

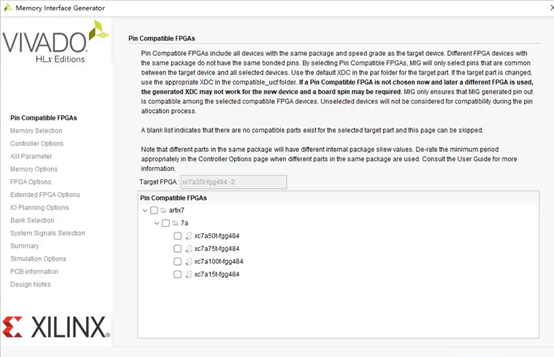

- Pin Compatible FPGAs:可以勾选一些兼容的型号器件,一般直接跳过。

点击Next后看到下一个界面:

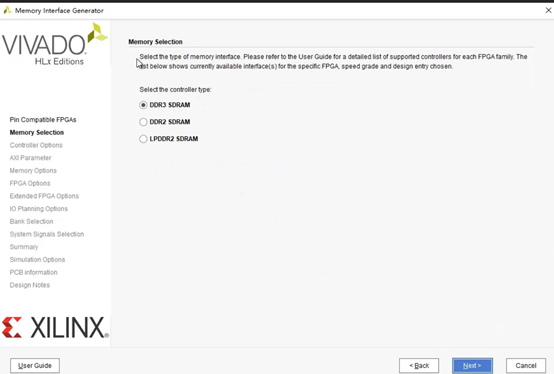

- Memory Selection:选择存储器类型。

点击Next后看到下一个界面:

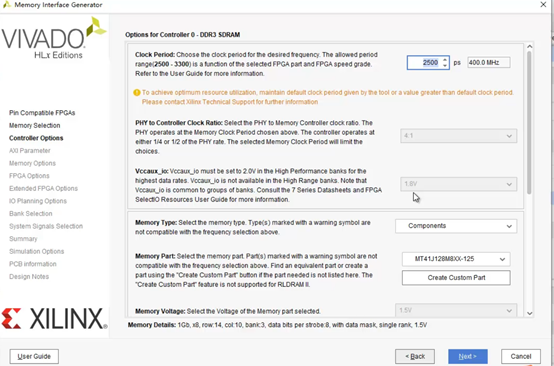

- Clock Period:接口时钟频率,用于FPGA输出给到DDR存储器时钟管脚的时钟,对于7系列的FPGA而言,这里最大可以设置到400MHz;

- PHY to Controller Clock Ratio:DDR时钟频率与FPGA用户逻辑时钟频率的比值;如果它的值是4:1,且DDR接口时钟频率为400MHz,那么FPGA逻辑读写的频率就是100MHz。

- Vccaux_io:电压电平,这个可以不用管;

- Memory Type:存储器类型,一般就选择Components,表示单颗粒的结构;

- Memory Part:存储器型号,每一种存储器型号的参数(频率、位宽、时序)都不一样,这个根据实际情况去选择;

- Memory Voltage:保持默认即可;

- Data Width:设置成存储器实际的数据位宽;

- ECC:不用管;

- Data Mask:使能Data Mask引脚,当Data Mask电平置高,数据无法写入;

- Number of Bank Machines:DDR控制器的Bank Machines个数设置,不一定与DDR存储器的Bank数量一致,可以保持默认;

- ORDERING:模式设置,如果是Normal模式,会允许控制器对用户发出的指令进行排序,从而得到更高效的利用,一般选择Strict模式,即不改变用户发出的指令顺序。

点击Next后看到下一个界面:

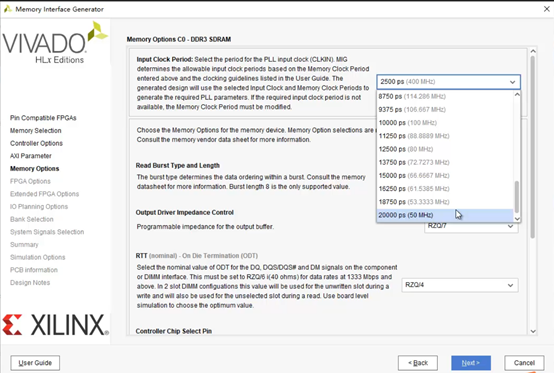

- Input Clock Period:输入系统时钟频率设置,这个时钟是提供给MIG IP的时钟;

- 其余按照默认即可。

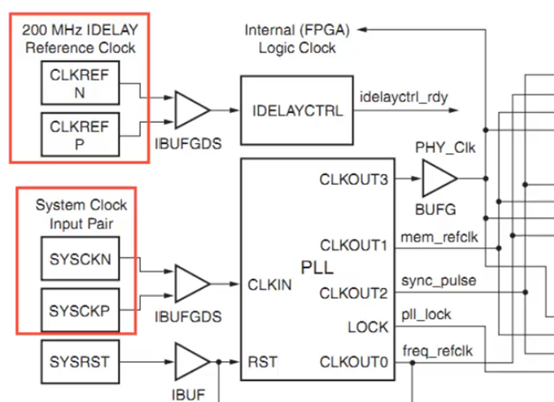

这里扩展说明一下,MIG IP核使用需要提供的时钟有两种,一个是Reference Clock;一种是System Clock。

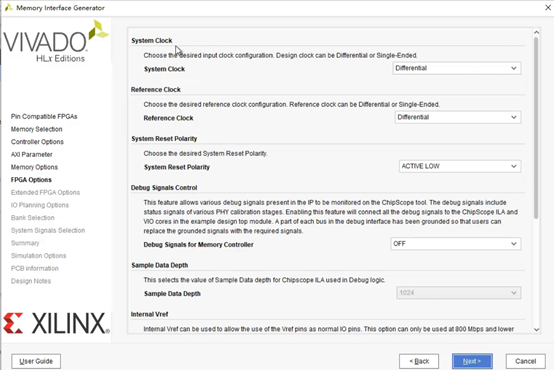

点击Next后看到下一个界面:

- System Clock:系统时钟,这里不是外部输入的时钟,因此只能选择No Buffer模式;

- Reference Clock:参考时钟。

- System Reset Polarity:复位的极性;

- Debug Signal for Memory Controller:调试信号,默认关掉就行;

- 其余保持默认即可。

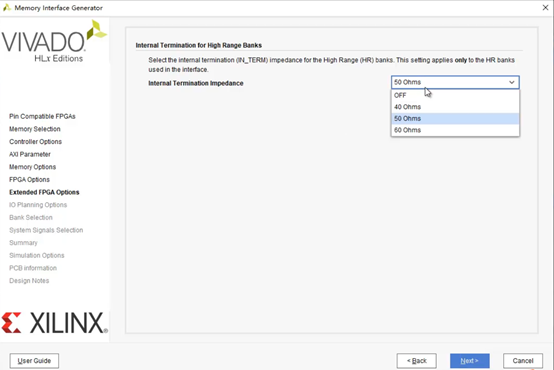

点击Next后看到下一个界面:

- Internal Termination Impedance:内部阻抗匹配。

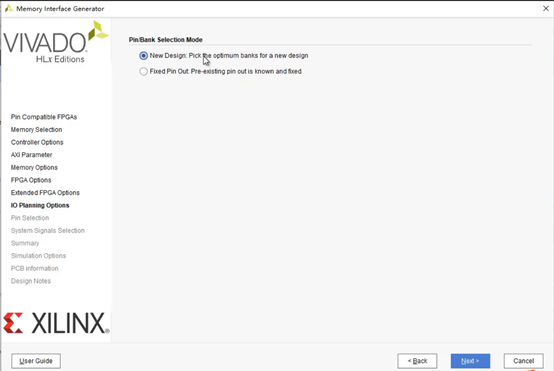

点击Next后看到下一个界面:

- Pin/Bank Selection Mode:引脚模式选择,一种是New Design模式,系统会帮你选择一个最佳的引脚设置;另一种是Fixed Pin Out模式,自定义选择引脚。

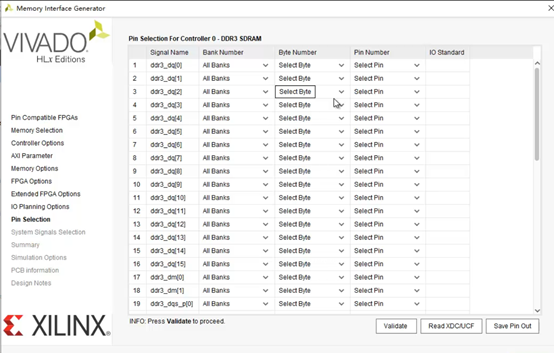

点击Next后看到下一个界面:

- Pin Selection For Controller:管脚选择。

后面的界面直接保持默认,最后选择Generate就可以了。

本期分享结束,感谢大家看完,私信我可获取相关详细资料!